Product Summary

The EP3C40F484C8 is an FPGA. It offers a unique combination of high functionality, low power and low cost. Based on Taiwan Semiconductor Manufacturing Company (TSMC) low-power (LP) process technology, silicon optimizations and software features to minimize power consumption, the EP3C40F484C8 provides the ideal solution for your high-volume, low-power, and cost-sensitive applications. The EP3C40F484C8 supports vertical migration that allows you to migrate your device to other devices with the same dedicated pins, configuration pins, and power pins for a given package-across device densities.

Parametrics

EP3C40F484C8 absolute maximum ratings: (1)Supply voltage for internal logic:–0.5V to 1.8V; (2)Supply voltage for output buffers:–0.5V to 3.9V; (3)Supply voltage (analog) for phase-locked loop (PLL) regulator: -0.5V to 3.75V; (4)Supply voltage (digital) for PLL:–0.5V to 1.8V; (5)DC input voltage:–0.5V to 3.95V; (6)DC output current, per pin: –25mA to 40mA; (7)Electrostatic discharge voltage using the human body model:±2000V; (8)Electrostatic discharge voltage using the charged device model:±500V; (9)Storage temperature:–65℃ to 150℃; (10)Operating junction temperature:–40℃ to 125℃.

Features

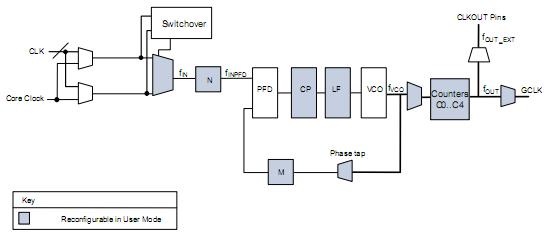

EP3C40F484C8 features: (1)TSMC low-power process technology; (2)Altera power-aware design flow; (3)Extended battery life for portable and handheld applications; (4)Reduced or eliminated cooling system costs; (5)Operation in thermally-challenged environments; (6)Design separation flow achieves both physical and functional isolation between design partitions ; (7)Provides a pass or fail indicator at every ED cycle; (8)Provides visibility over intentional or unintentional change of configuration random access memory (CRAM) bits; (9)Five outputs per PLL; (10)Cascadable to save I/Os, ease PCB routing, and reduce jitter; (11)Dynamically reconfigurable to change phase shift, frequency multiplication or division, or both, and input frequency in the system without reconfiguring the device; (12)Remote system upgrade without the aid of an external controller; (13)Dedicated cyclical redundancy code checker circuitry to detect single-event upset (SEU) issues; (14)Nios II embedded processor for Cyclone III device family, offering low cost and custom-fit embedded processing solutions.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

EP3C40F484C8 |

|

IC CYCLONE III FPGA 40K 484FBGA |

Data Sheet |

|

|

||||||

|

EP3C40F484C8N |

|

IC CYCLONE III FPGA 40K 484FBGA |

Data Sheet |

|

|

||||||

(Singapore)

(Singapore)