Product Summary

The EPC2TC32 is an FPGA. It allows the user to initiate configuration of the FPGA via an additional pin, nINIT_CONF. The nINIT_CONF pin of the EPC2TC32 can be connected to the nCONFIG of the FPGA(s), which allows the INIT_CONF JTAG instruction to initiate FPGA configuration. The INIT_CONF JTAG instruction causes the EPC2TC32 to drive nINIT_CONF low, which in turn pulls nCONFIG low. Pulling nCONFIG low on the FPGA will reset the device.

Parametrics

EPC2TC32 absolute maximum ratings: (1)Supply voltage: –2.0V to 7.0V; (2)DC input voltage:–2.0V to 7.0V; (3)DC VCC or ground current:50mA; (4)DC output current, per pin: –25mA to 25mA; (5)Power dissipation:250mW; (6)Storage temperature:–65℃ to 150℃; (7)Ambient temperature:–65℃ to 135℃; (8)Junction temperature:135℃.

Features

EPC2TC32 features: (1)Easy-to-use 4-pin interface to Altera FPGAs; (2)Low current during configuration and near-zero standby current ; (3)5.0-V and 3.3-V operation; (4)Software design support with the Altera Quartus II and MAX+PLUS II development systems for Windows-based PCs as well as Sun SPARCstation, and HP 9000 Series 700/800; (5)Programming support with the Altera Programming Unit (APU) and programming hardware from Data I/O, BP Microsystems, and other third-party programmers ; (6)Available in compact plastic packages:8-pin plastic dual in-line package (PDIP), 20-pin plastic J-lead chip carrier (PLCC)package, 32-pin plastic thin quad flat pack (TQFP) package; (7)5.0-V and 3.3-V in-system programmability (ISP) through the built-in IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface; (8)Built-in JTAG boundary-scan test (BST) circuitry compliant with IEEE Std. 1149.1; (9)ISP circuitry is compatible with IEEE Std. 1532.

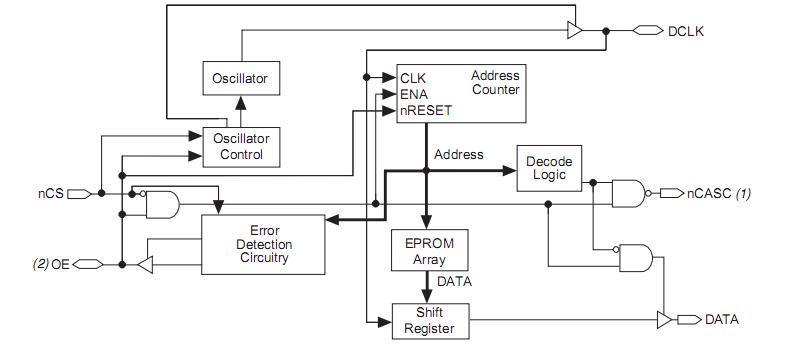

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

EPC2TC32 |

Altera |

IC CONFIG DEVICE 1.6MBIT 32-TQFP |

Data Sheet |

|

|

||||||

|

EPC2TC32N |

Altera |

IC CONFIG DEVICE 1.6MBIT 32-TQFP |

Data Sheet |

|

|

||||||

(Singapore)

(Singapore)