Product Summary

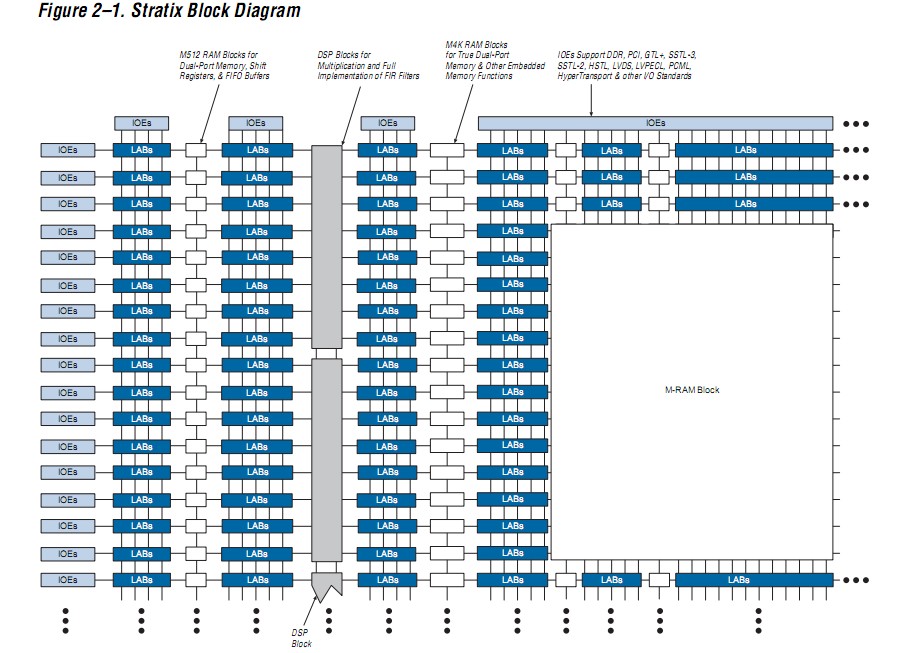

The EP1S60F1020C7 is a Stratix logic array which contains a two-dimensional row- and column-based architecture to implement custom logic. A series of column and row interconnects of varying length and speed provide signal interconnects between logic array blocks (LABs), memory block structures, and DSP blocks. The logic array consists of LABs, with 10 logic elements (LEs) in each LAB. An LE is a small unit of logic providing efficient implementation of user logic functions. LABs are grouped into rows and columns across the EP1S60F1020C7.

Parametrics

EP1S60F1020C7 absolute maximum ratings: (1)Supply voltage With respect to ground:–0.5 to 2.4 V; –0.5 to 4.6 V; (2)DC input voltage: –0.5 to 4.6 V; (3)DC output current, per pin: –25 to 40 mA; (4)Storage temperature No bias: –65 to 150℃; (5)Junction temperature BGA packages under bias: 135 ℃.

Features

EP1S60F1020C7 features: (1)10,570 to 79,040 LEs; see Table 1–1; (2)Up to 7,427,520 RAM bits (928,440 bytes) available without reducing logic resources; (3)TriMatrixTM memory consisting of three RAM block sizes to ; (4)implement true dual-port memory and first-in first-out (FIFO) buffers; (5)High-speed DSP blocks provide dedicated implementation of multipliers (faster than 300 MHz), multiply-accumulate functions, and finite impulse response (FIR) filters; (6)Up to 16 global clocks with 22 clocking resources per device region; (7)Up to 12 PLLs (four enhanced PLLs and eight fast PLLs) per device provide spread spectrum, programmable bandwidth, clock switch-over, real-time PLL reconfiguration, and advanced multiplication and phase shifting; (8)Support for numerous single-ended and differential I/O standards; (9)High-speed differential I/O support on up to 116 channels with up to 80 channels optimized for 840 megabits per second (Mbps); (10)Support for high-speed networking and communications bus standards including RapidIO, UTOPIA IV, CSIX, HyperTransportTM technology, 10G Ethernet XSBI, SPI-4 Phase 2 (POS-PHY Level 4), and SFI-4; (12)Differential on-chip termination support for LVDS; (13)Support for 66-MHz PCI (64 and 32 bit) in -6 and faster speed-grade devices, support for 33-MHz PCI (64 and 32 bit) in -8 and faster speed-grade devices; (14)Support for 133-MHz PCI-X 1.0 in -5 speed-grade devices; (15)Support for 100-MHz PCI-X 1.0 in -6 and faster speed-grade devices; (16)Support for 66-MHz PCI-X 1.0 in -7 speed-grade devices.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

EP1S60F1020C7 |

|

IC STRATIX FPGA 60K LE 1020-FBGA |

Data Sheet |

|

|

||||||

|

EP1S60F1020C7N |

|

IC STRATIX FPGA 60K LE 1020-FBGA |

Data Sheet |

|

|

||||||

(Singapore)

(Singapore)